FIFOのバンク数は、2つ、3つ、4つをセレクトできます.

疑問: このFIFOバンクって、多数の短いパケットを送信したらどのように働くのだろう?

具体的にはこういう疑問です.

たった5バイトしかデータ転送しないとして、512BYTEがオーバーフローするまでじーっと黙っているのだとすると、103回データ転送しないとFIFOが出力移行しません.まぁそりゃないだろと思います.たとえ5バイトでも、一回受信したら律儀に5バイトを出力するんだろと思う.

しかし、だとすると、ゴージャスな4バンク構成にしても、たった5x4=20バイト溜まっただけでFIFOがオーバーフロー間際の断末魔になってしまいます.それも悲しいように思います.

そこで実機で確かめました.

↓たった5バイトを転送しても、一瞬でデータは出ていってしまいますので観測しにくい.そこで、RDY0を発生させる回路に細工してRDY0をON/OFFできるようにしました.SWでザックリ切断です.

FX2LPでdownloadするプログラムのプロジェクトファイルはこちらです.

フォルダ中には、バンク数違いの3つのプロジェクトが入っています.

FIFO2bank.Uv2 → EP2のFIFOが、512BYTE x 2バンク

FIFO3bank.Uv2 → EP2のFIFOが、512BYTE x 3バンク

FIFO4bank.Uv2 → EP2のFIFOが、512BYTE x 4バンク

バンク数によって各設定の異なる部分は、バンク数設定と、念のためEP468を殺すと、リセットをバンク数回やる、の2点です.EP246を殺すのは、EP2がEP468のFIFOエリアを侵食するから.

2バンク設定

EP2CFG = 0xA2; // EP2 is DIR=OUT, TYPE=BULK, SIZE=512, BUF=2x

SYNCDELAY;

FIFORESET = 0x80; // Reset the FIFO

SYNCDELAY;

FIFORESET = 0x82;

SYNCDELAY;

FIFORESET = 0x00;

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF0)

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF1)

SYNCDELAY;

3バンク設定

EP2CFG = 0xA3; // EP2 is DIR=OUT, TYPE=BULK, SIZE=512, BUF=3x

SYNCDELAY;

EP4CFG = 0; ←念のためEP4を殺しておく

SYNCDELAY;

EP6CFG = 0; ←念のためEP6を殺しておく

SYNCDELAY;

EP8CFG = 0; ←念のためEP8を殺しておく

SYNCDELAY;

FIFORESET = 0x80; // Reset the FIFO

SYNCDELAY;

FIFORESET = 0x82;

SYNCDELAY;

FIFORESET = 0x00;

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF0)

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF1)

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF2)

SYNCDELAY;

4バンク設定

EP2CFG = 0xA0; // EP2 is DIR=OUT, TYPE=BULK, SIZE=512, BUF=4x

SYNCDELAY;

EP4CFG = 0; ←念のためEP4を殺しておく

SYNCDELAY;

EP6CFG = 0; ←念のためEP6を殺しておく

SYNCDELAY;

EP8CFG = 0; ←念のためEP8を殺しておく

SYNCDELAY;

FIFORESET = 0x80; // Reset the FIFO

SYNCDELAY;

FIFORESET = 0x82;

SYNCDELAY;

FIFORESET = 0x00;

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF0)

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF1)

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF2)

SYNCDELAY;

OUTPKTEND = 0x82; // skip EP2 FIFO data (BUF3)

SYNCDELAY;

-----

以下が動作確認結果です.

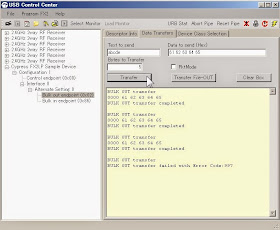

programのdownloadにも使っている「USB Control Center」というアプリを使うと、任意のバイト数のデータ転送ができます.それを利用して、2バンク、3バンク、4バンクそれぞれを動かします.

なお、上の回路図のRDY0のSWをオフしておきます.するとデータがFIFOにブタ積みされても、便秘状態なのでデータが排出されません.この実験では強制便秘にしています.

↓まず最初に、2バンクで動作させたのがこの結果.abcdeという文字が見えますが、このabcdeが転送したい5バイトです.Transferボタンを1回押すと、5バイト送信される仕組みです.

右のペインには、Transfer completeが2回表示され、3回目でTransfer Failedになっています.これは何が起きているのかというと、FX2LPの起動直後にFIFOが2バンクとも空っぽなので、2回までは耐えられる.でも3回目で「お漏らし」エラーを出してます.

↓つぎは3バンクでのお試し結果.空っぽのFIFOが3バンクあるので、3回目までは耐えて、4回目で「お漏らし」エラーしてます.

↓最後は4バンクでのお試し結果.空っぽのFIFOが4バンクあるので、4回目までは耐えて、5回目で「お漏らし」しちゃってます.

以上より、FX2LPのFIFOバンクはこのように動作するんだとわかりました.

たとえ5バイトのデータ転送でも、その都度出力移行する.

短いデータを何発も転送すると、すぐにFIFOがオーバーフローしてしまうリスクあり.

うーん、やっぱりそうか、、、そうなのか、、、

その11へ その13へ

かしこ

INDEXページへ

https://hirasakausb.blogspot.com/2019/03/ez-usb-fx2lp-index.html

EP2CFG = 0xA2; // EP2 is DIR=OUT, TYPE=BULK, SIZE=512, BUF=2x

返信削除の様な記述はコンパイルせずに(オブジェクトにしない)暗算的に表現する方法は有りましたっけ?

EP2CFG =(EP2 is DIR=OUT, TYPE=BULK, SIZE=512, BUF=2x・・の様な

そうですねぇ、このLSIにはそういう人間が読みやすい関数ライブラリは提供されていないので、16進数のマジックナンバーがたくさん出てきます.なので、ソースを読むときはレジスタ表を首っ引きになります.

削除